Military-Grade PCBs zeichnen sich durch hohe klimatische Ansprüche aus. Vor allem aber müssen sie über Jahrzehnte hinweg zuverlässig arbeiten – oft ohne Wartungsmöglichkeit. Der Hardware-Entwicklung werden daher früh im Prozess enge Grenzen gesetzt.

In diesem Artikel beleuchten wir die technischen Standards und Best Practices, die PCB-Design für militärische Anwendungen prägen. Von den grundlegenden Normen über Materialauswahl bis hin zu spezifischen Design-Regeln zeigen wir, worauf es bei der Entwicklung von Elektronik für die Rüstungsindustrie wirklich ankommt. Sie gelten zusätzlich zu den Anforderungen an Exportkontrolle und die Ausfuhr von Rüstungsgütern sowie Anforderungen regulatorischer Natur der NATO-Rüstungsindustrie im Allgemeinen.

Inhalt

Kriterien aus der MIL-PRF-31032 für MIL Elektronik

MIL-PRF-31032 ist die zentrale Performance-Spezifikation für starre militärische PCBs und betrifft weitestgehend Produktions- und Verarbeitungsanforderungen. Diese Norm etabliert nicht nur allgemeine Leistungsanforderungen, sondern reguliert, welche Materialien verwendet werden dürfen, wie Fertigungsprozesse auszusehen haben und welche Qualitätssicherungsmaßnahmen zwingend erforderlich sind. Im Gegensatz zu kommerziellen Standards, die gewisse Toleranzen und Abweichungen zulassen, verfolgt MIL-PRF-31032 eine Zero-Defect-Philosophie. Unter anderem gilt es klare Anforderungen an Board- und Verarbeitungsgeometrien zu setzen, wie zum Beispiel Platings, Drills oder Rings. Ergänzt wird MIL-PRF-31032 durch MIL-PRF-50884 für spezifische Fertigungsaspekte und MIL-PRF-55110 für zusätzliche Qualitätsanforderungen. Zusammen bilden diese Spezifikationen ein engmaschiges Regelwerk, das jeden Aspekt der PCB-Entwicklung und -Fertigung abdeckt.

In der MIL-PRF-31032 werden Punkte wie ionische Reinheit, Haftfestigkeit, Zugfestigkeit sowie Widerstand gegen Feuchtigkeit und thermische Belastung spezifiziert. Ferner legt er fest, dass Materialien, Plattierung und Verarbeitung reproduzierbar, belastbar und für den Einsatz unter anspruchsvollen Umweltbedingungen geeignet sein müssen. Jene Norm ist also weniger eine Design-Maßgabe, sondern zielt v.a. auf Herstellungs- und Validierungsprozesse. Engineering-Unternehmen berücksichtigen im Rahmen der Norm Via-Dimensionen, Stackups und Abstände von Leiterbahnen zueinander und zu Außendimensionen.

Plated-through hole accept-reject criteria. The test specimen has soldered successfully if solder has risen in all plated-through holes. The solder shall have fully wetted the walls of the plated-through hole. There shall be no exposed base metal or any nonwetting on any plated-through hole.

PRF-31032 zu beschichteten Durchgangskontaktierungen

IPC-A-600 Class 3

IPC-A-600 ist der weltweit anerkannte Standard zur Bewertung der Qualität elektronischer Baugruppen. Er beschreibt objektive Akzeptanzkriterien für Lötverbindungen, mechanische Befestigungen, Oberflächenbeschaffenheiten, Bauteilplatzierung und weitere Merkmale, die für die Zuverlässigkeit elektronischer Produkte relevant sind.

Der Standard definiert drei Klassen, die unterschiedliche Anforderungen an Funktionssicherheit und Einsatzumgebung stellen:

- Klasse 1 – Allgemeine Elektronik

Produkte mit begrenzten Anforderungen an Lebensdauer und Zuverlässigkeit. - Klasse 2 – Betriebsgeräte mit höheren Anforderungen

Geräte, die eine stabile Funktion über eine längere Zeit voraussetzen, z. B. Industriesteuerungen, Kommunikationsgeräte. - Klasse 3 – Hochzuverlässige Elektronik

Anwendungen mit kritischen Anforderungen, bei denen Ausfälle nicht tolerierbar sind, z. B. Luft- und Raumfahrt, Medizintechnik, Verteidigung.

Während MIL-Standards primär für US-amerikanische Militärprojekte gelten, haben sich die IPC-Standards international als Referenz etabliert. Für militärische Anwendungen ist ausschließlich IPC Class 3 relevant.

Um die IPC-A-600 herum reihen sich eine ganze Reihe von Standards, die Akzeptanzkriterien an das fertig bestückte Board sowie das Design der Leiterplatte festlegen. Diese Standards zu erfüllen ist in der Regel gemeinsame Aufgabe von Entwicklern, Fertigern, Bestückern und Inverkehrbringern.

Beispielhaft lohnt sich ein Blick in den IPC-A-610-Standard. IPC-A-610 definiert Abnahmekriterien für elektronische Baugruppen, ohne selbst Fertigungsprozesse oder Designregeln vorzugeben. Jedes Merkmal wird in „anzustreben“, „zulässig“, „Fehler“ und „Prozessindikator“ eingeteilt, ergänzt um Regeln für kombinierte, nicht spezifizierte und Sonderzustände.

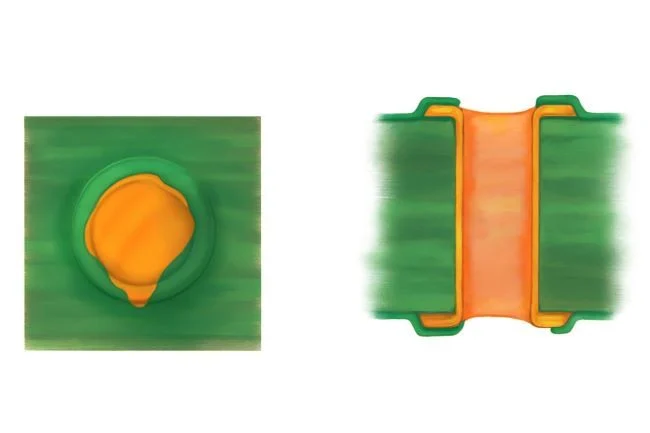

Beispielhaft lässt sich das an runden oder geprägten Anschlüssen zeigen: IPC-A-610 legt für diese Anschlüsse eine minimale Lötstellenhöhe an der Ferse (F) fest, die von der Produktklasse abhängt. Für Klasse 1 muss die Lötstelle mindestens den Mittelpunkt der äußeren Anschlussbiegung erreichen, für Klasse 2 mindestens Lotspaltdicke G + 50 % der Anschlussdicke T und für Klasse 3 Lotspaltdicke G + 100 % der Anschlussdicke T. Dadurch wird das Klassensystem auf eine konkrete, messbare Geometrie heruntergebrochen, an der sich Fertigung, Inspektion und Nacharbeit orientieren können.

Ferse (F) muss mindestens den Mittelpunkt der äußeren Anschlussbiegung überschreiten → sonst Fehler. - Klasse 1: Sichtbar gute Benetzung erforderlich

- Klasse 2: Mindesthöhe F ≥ G + 50 % T

- Klasse 3: Mindesthöhe F ≥ G + 100% TUnterschreitung der jeweiligen Mindesthöhe → Fehler in Klasse 2 bzw. 3

Beispielanforderung der IPC-A-610 für MIL Elektronik

IPC-Anforderungen für Layout und Schematics

Für die Entwicklung moderner Leiterplatten somit existiert eine Vielzahl an IPC-Standards. Nicht jede Norm ist für jedes Design relevant, aber einige Dokumente bilden den Kern dessen, was Designer und Fertiger täglich benötigen.

Viele dieser Standards sind verhältnismäßig spezifisch und entsprechend umfangreich. Für PCB-Designer bedeutet das: Die wichtigsten Vorgaben sollten direkt in den Designregeln hinterlegt werden, damit Layout, Fertigung und spätere Qualitätsprüfung auf einem konsistenten Regelwerk basieren.

Zu den häufig genutzten und relevanten IPC-Standards gehören:

- IPC-A-600: Abnahmekriterien, inklusive der Klassifizierung in IPC Class 1, 2 und 3

- IPC-2221: generische Design- und Leistungsanforderungen für Leiterplatten

- IPC-4101: Materialvorgaben für Laminat- und Prepreg-Typen sowie Stackup-Definitionen

- IPC-2152: Strombelastbarkeit von Leiterbahnen

- IPC-4761: Kategorisierung und Designrichtlinien für Via-Abdeckungen und Via-Schutzarten

- IPC-6012: Fertigungs- und Qualitätsanforderungen an starre Leiterplatten

- IPC-7351: Footprint- und Land-Pattern-Design für SMD-Bauteile

- IPC-1752A: Vorgaben für Materialdeklaration und Datenaustausch über Inhaltsstoffe

- IPC-6012E: Anforderungen an Restringe und mechanische Stabilität

- IPC-2581: herstellerunabhängiges, datenkonsistentes Austauschformat für Fertigungsdaten, das alle Fertigungsinformationen in einem strukturierten Modell transportiert.

Typische Praktiken für Military und IPC-Class 3 Designs

Class-3-Produkte erfordern erhöhte mechanische Stabilität, definierte Belastbarkeit und präzise Fertigung. Dazu gehören insbesondere: Teardrops an Übergängen zwischen Leiterbahn und Via/Pad, um mechanische Ausbrüche zu vermeiden. Anforderungen an Restringe gemäß IPC-6012E, um die Via-Struktur gegen thermische und mechanische Belastungen zu stabilisieren. Kontrollierte Impedanz und Signalintegrität, insbesondere bei Hochgeschwindigkeits- oder HF-Schaltungen durch definierte Leiterbahnbreiten, Abstände und Stackup-Abstimmung. Wärmemanagement, z. B. über thermisch optimierte Layer-Aufbauten, Heat-Spreader, Via-Arrays oder thermische Entlastungsflächen. Diese Maßnahmen sind typisch für hochzuverlässige Baugruppen und richten sich klar an Anwendungen, bei denen elektrische und mechanische Stabilität im Vordergrund stehen – etwa in Luftfahrt, Verteidigung, Industrieautomation oder anspruchsvollen Sensor- und Steuergeräten.

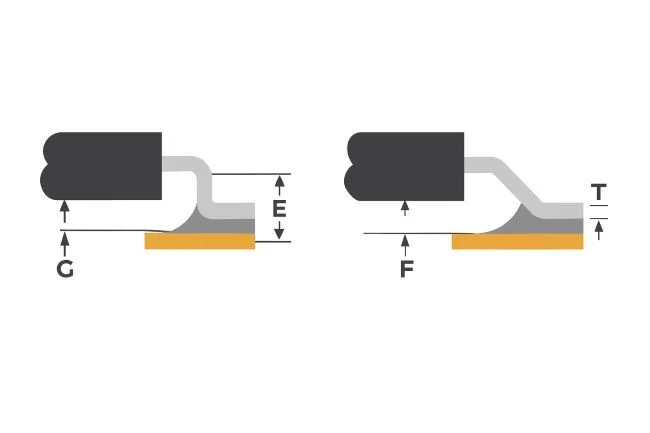

Stack-up-Symmetrie

Ein vollständig asymmetrischer Stack-up ist der Feind jeder hochwertigen PCB. Er führt zu Verzug (Warpage), beeinträchtigt die mechanische Stabilität und kann die Impedanz unkontrollierbar machen. Für Class 3 PCBs ist ein symmetrischer Aufbau in der Regel erstrebenswert. Die Symmetrie bezieht sich sowohl auf die Lagendicken als auch auf die Kupfergewichte. Wenn auf der Oberseite eine Signallage mit 1 oz Kupfer liegt, sollte auf der Unterseite in entsprechender Position ebenfalls eine Signallage mit 1 oz Kupfer sein. Diese Balance gewährleistet gleichmäßige Impedanz und minimiert Crosstalk.

Power- und Ground-Planes sollten direkt nebeneinander platziert werden. Diese Anordnung schafft einen großflächigen Kondensator, der hochfrequente Störungen effektiv unterdrückt und elektromagnetische Interferenzen (EMI) minimiert.

Signal-Layer werden vorzugsweise neben Ground-Planes angeordnet. Dies schafft kürzere Rückstrompfade und eine engere Kopplung, was die Signal-Integrität verbessert und Abstrahlungen reduziert. In einer typischen 8-Lagen-Struktur könnte dies so aussehen:

- Signal (Top)

- Ground

- Signal

- Power

- Ground

- Signal

- Ground

- Signal (Bottom)

Eine grafische Darstellung wie folgt:

Teardrops

Teardrops sind tropfenförmige Kupferverstärkungen an der Übergangsstelle zwischen Leiterbahn und Pad oder Via. In militärischer Elektronik werden sie eingesetzt, um die mechanische Robustheit solcher Übergänge zu erhöhen und Fertigungstoleranzen besser abzufangen. Besonders relevant sind Teardrops im Bereich von Fanouts, also beim Herausführen von Signalen aus feinen Bauteilanschlüssen – etwa bei BGAs oder hochpoligen ICs. Beim Fanout entstehen häufig kurze Leiterbahnsegmente zwischen Pad und Via, die empfindlich gegenüber Bohrversatz oder mechanischen Belastungen sein können.

Durch die vergrößerte Kupferfläche am Übergang stabilisieren Teardrops diese kritischen Bereiche im Layout. Sie reduzieren die Gefahr, dass sich Leiterbahnen durch Bohrtoleranzen, Vibration oder thermische Zyklen vom Via lösen. Gleichzeitig verteilen sie mechanische Spannungen gleichmäßiger im Kupfer. Teardrops reduzieren die mechanische Belastung an Via-Bohrungen, wodurch das Risiko von Mikrorissen oder unterbrochenen Verbindungen in hochbelasteten elektronischen Systemen verringert wird.

Anforderungen an Annular Rings

In militärischen Elektroniksystemen gelten für Leiterplatten deutlich strengere Anforderungen an den Annular Ring als in vielen kommerziellen Anwendungen. Der Annular Ring bezeichnet die ringförmige Kupferfläche um eine Bohrung oder Via. Diese Fläche stellt sicher, dass trotz Bohrtoleranzen, Lagenversatz oder Fertigungsstreuungen eine zuverlässige elektrische Verbindung zwischen Pad und Bohrung erhalten bleibt. In MIL-Umgebungen – etwa in Luftfahrt-, Fahrzeug- oder Verteidigungssystemen – sind Leiterplatten starken mechanischen und thermischen Belastungen ausgesetzt. Deshalb werden größere Mindestbreiten des Annular Rings gefordert, um Ausfälle durch Ausbrüche, unvollständige Durchkontaktierungen oder mechanische Spannungen zu vermeiden. Besonders bei Through-Hole-Bauteilen, Steckverbindern und mechanisch belasteten Baugruppen ist ein großzügig dimensionierter Annular Ring ein wichtiges Robustheitsmerkmal.

Connector Specifications

Eine weitere typische Praxis im Umfeld von IPC Class 3 ist der gezielte Einsatz von U.S. Military Connector Specifications (MIL-DTL) – abhängig davon, ob Schnittstellen nach außen in eine raue Einsatzumgebung geführt werden oder ausschließlich innerhalb geschützter Systeme arbeiten. Für robuste Außenanwendungen kommen vor allem rugged circular connectors wie die MIL-DTL-38999-Familie zum Einsatz. Diese Steckverbinder sind für extreme mechanische Belastungen, Feuchtigkeit, Vibration, Schock, Staub und große Temperaturbereiche ausgelegt und werden typischerweise für außenliegende Verbindungen im militärischen Umfeld, etwa bei Soldatensystemen, Fahrzeugen, Sensorplattformen oder Waffensystemen verwendet.

Demgegenüber stehen kompakte Hochdichte-Stecksysteme für interne Verbindungen, etwa MIL-DTL-24308 (D-Sub-Steckverbinder) und MIL-DTL-32139 (Nanominiature-Connector). Diese kommen bei Board-to-Board-, FPC-, Backplane- oder Board-to-Module-Verbindungen zum Einsatz, also dort, wo die Verbindung mechanisch geschützt „behind-panel“ oder in gekapselten Baugruppen liegt. Während außenliegende Steckverbinder primär auf Umweltrobustheit, Verriegelungssicherheit und Schutz vor Fehlstecken optimiert sind, stehen bei internen MIL-Stecksystemen Packungsdichte, Schockfestigkeit, Kontaktstabilität und reproduzierbare elektrische Eigenschaften im Vordergrund.

Die Steckverbindernormen sind wie folgt:

- MIL-DTL-38999: Rugged circular connector für außenliegende Verbindungen unter Schock, Vibration, Feuchte.

- MIL-DTL-26482: Robuster Miniatur-Rundsteckverbinder für raue Umgebungen.

- MIL-DTL-24308: D-Sub für geschützte Board-to-Board- und Panel-Verbindungen.

- MIL-DTL-32139: Nanominiature-Connector für hochdichte FPC- und Modul-Verbindungen.

- MIL-DTL-83513: Micro-D für kompakte, vibrationsfeste Signalverbindungen.

Eurokarten- und Rack-Formate

Militärische Elektroniksysteme („MIL Elektronik“) werden häufig in modularen Einschubsystemen aufgebaut, bei denen Leiterplatten als standardisierte Karten in ein Rack oder Chassis eingeschoben werden. Eine zentrale Rolle spielen dabei Eurokartenformate nach der Normenreihe IEC 60297. Diese Norm definiert die mechanischen Abmessungen von Baugruppenträgern, Frontplatten und Leiterkarten für 19-Zoll-Racks. Typische Formate sind 3U (ca. 100 × 160 mm) und 6U (ca. 233 × 160 mm). Die Karten werden über Backplanes miteinander verbunden und lassen sich als modulare Baugruppen austauschen. Dadurch können Systeme aus verschiedenen Funktionskarten aufgebaut werden, etwa Prozessor-, Kommunikations- oder I/O-Karten.

In vielen militärischen und industriellen Systemen kommen zusätzlich Busstandards zum Einsatz, die auf diesen Eurokartenformaten aufbauen. Beispiele sind VMEbus, CompactPCI oder VPX. Diese Standards definieren neben den mechanischen Abmessungen auch Steckverbinder, Backplane-Topologien und elektrische Schnittstellen. Insbesondere VPX wurde für militärische Anwendungen entwickelt und erlaubt Hochgeschwindigkeits-SerDes-Verbindungen sowie robuste Steckverbinder für Umgebungen mit Vibration, Temperaturwechseln und mechanischer Belastung.

Fazit

PCB-Design für die Rüstungsindustrie ist eine herausfordernde Disziplin für Systemingenieure, Hardware-Designer und Qualitätsprüfung. Die Prinzipien, die wir in diesem Artikel beleuchtet haben – von der Materialauswahl über Via-Design bis hin zu Thermal Management – sind das Ergebnis jahrzehntelanger Erfahrung und unzähliger Lektionen aus dem Feld. Sie repräsentieren den Stand der Technik in Sachen Zuverlässigkeit und Langlebigkeit. Für Entwicklungsdienstleister und Ingenieurbüros, die in diesem Sektor tätig sind oder werden wollen, ist die Beherrschung dieser Standards nicht optional.